- ナレッジセンター

- 匠コラム

Mipsology Zebra:FPGAを使用した高効率な推論プラットフォーム

- 匠コラム

- AI

ビジネス開発本部 第1応用技術部

第1チーム

Ryosunata Suhartono

はじめに

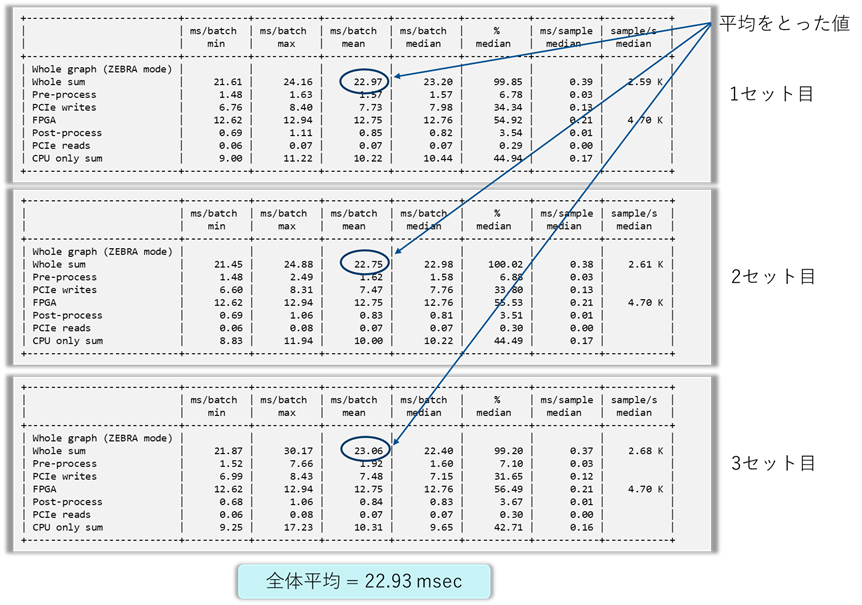

世の中にAIを活用したテクノロジーが浸透し、画像推論を使用した様々なアプリケーションが普及しました。ビルの監視カメラの映像を分析するものや、スマートフォン等の端末で動作するアプリケーションまであります。これらのアプリケーションで推論を行う演算をソフトウェア的にCPUで実施しているものだけでなく、GPUやFPGAといったハードウェアにオフロードして行うシステムも出ています。小型の端末では、それ専用のチップで行っているものも出てきました。

今回のコラムでは、映像データを高効率で推論するシステムとして評価するため、CPUとFPGAオフロードを比較して得た検証結果を共有します。両者で同じ計算をさせて、制度の違いや計算に費やした消費電力の違いを評価してみました。

検証の方法と条件

今回の検証ではMipsology社のアプリケーションソフトウェアZebraを使用しました。ソフトウェアのバージョンはV2020.02.1を使用しています。そのほかの検証環境については以下にまとめています。

使用したサーバDell Poweredge R7515

CPU : AMD EPYC 7302P 16-Core Processor

Memory : 64GB x2 DIMM (128GB)

FPGA : Alveo U250(550MHzで動作)

OS : Ubuntu 18.04.1 LTS x86_64

Kernel : 4.15.0-101-generic

検証条件

- モデルはResNet50を使用

- 1セットで、60枚の画像を50回batch計算実行(1 batchを1周期とします)

- 入力イメージサイズは224x224 pixel x 3チャンネルを使用

- 評価対象はImageNetを使用

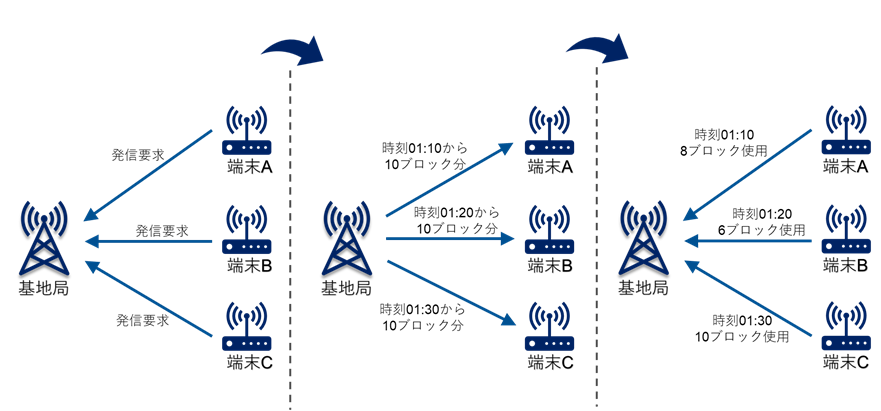

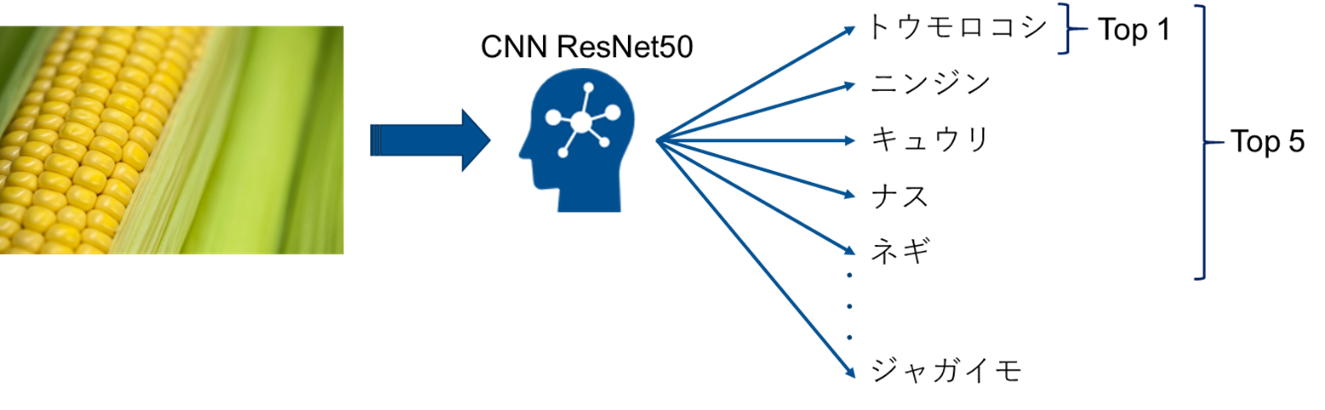

今回の検証内容をイメージした絵を次の「図1.各手法の実行イメージ」に描きました。

図1.各手法の実行イメージ

パフォーマンス測定

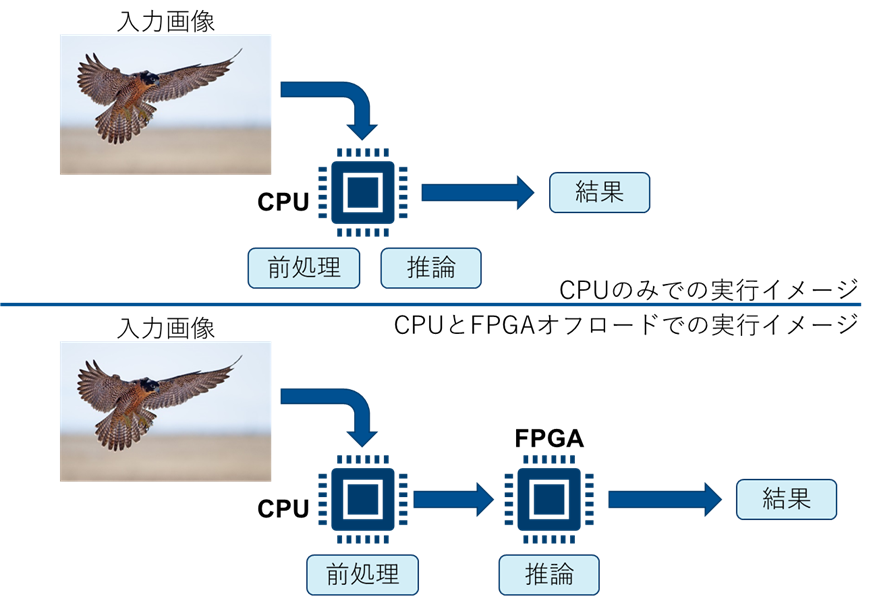

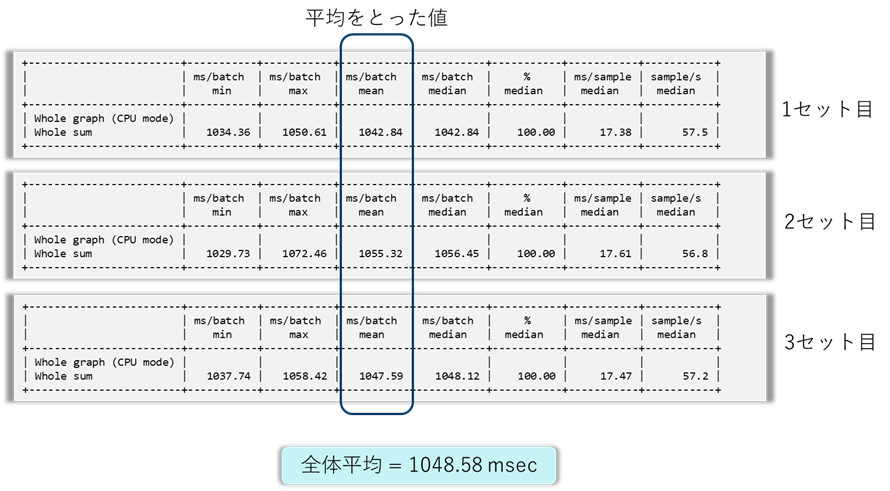

パフォーマンス測定の検証では、各batchでの計算に要した時間を計測しています。CPUのみでの実行結果とCPUとFPGAオフロードを活用した場合の計算結果で、それぞれ3セット実施した結果を取得しました。最終的には3セットで得られた結果を平均化して、それぞれの結果としています。具体的な結果は「図2.CPUのみでの測定結果」と「図3.CPU+FPGAオフロードでの測定結果」となります。

図2.CPUのみでの測定結果

図3.CPU+FPGAオフロードでの測定結果

パフォーマンスの測定結果から分かったこととして、FPGAオフロードを使用した計算のほうが、CPUのみでの計算よりも46倍速い結果となりました。

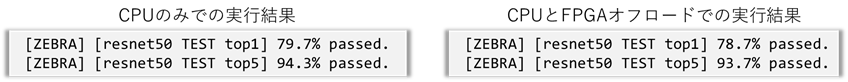

精度の測定

計算精度についてはどれぐらいの差が出るのかも確認しました。精度の導き出し方については、ResNet50の推論結果から、正解が最も高い確率(Top1)として導き出せているか、および最も確率の高い結果から5番目の確率(Top5)以内に正解が入っている割合を比較します。イメージしやすいように「図4.結果の読み取り方」にイメージを描きました。

図4.結果の読み取り方

CPUのみでの実施結果と、CPUとFPGAオフロードを活用した実施結果を「図5.精度の測定結果」に記載しました。

図5.精度の測定結果

図5の結果から読み取れることとしては、FPGAオフロードを活用した場合で、Top1の精度は1%の低下、Top5の精度は0.6%の低下にそれぞれ抑えられていることがわかりました。

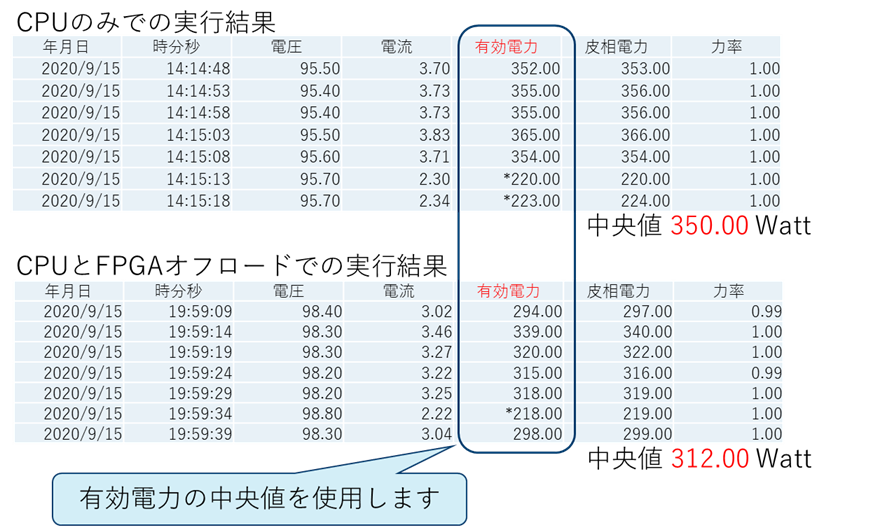

消費電力の測定

推論の計算を実施する際の消費電力を比較する検証を行いました。この検証では、同じ計算量での比較を条件として、計算にかかった時間と計算時に消費される電力を掛け合わせた結果を比較することにしました。

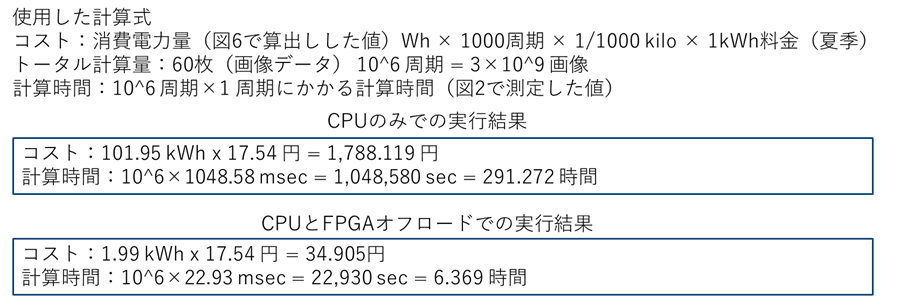

計算に使用する消費電力は「図6.消費電力の求め方」に記載します。同じ計算量を計算した際の比較を「図7.消費電力量の比較」に記載しました。そして、最終的には東京電力エナジーパートナー様が出している業務用電力プランからコストに換算した結果を比較した結果を「図8.コストパフォーマンスの比較」にて算出しました。

図6.消費電力の求め方

消費電力を求める際に、推論の計算を “CPUのみでの実行結果” と “CPUとFPGAオフロードでの実行結果” をそれぞれ2時間での連続した計算を実施して消費電力を計測しました。今回、実行した計算プログラムの仕様として、計算の周期と周期の間にデータの整理といった、軽いプロセスが存在します。そのため “ * ” 印のついた値のように計測結果に外れ値が混ざっています。よって、有効電力の中央値を消費電力の基準としました。

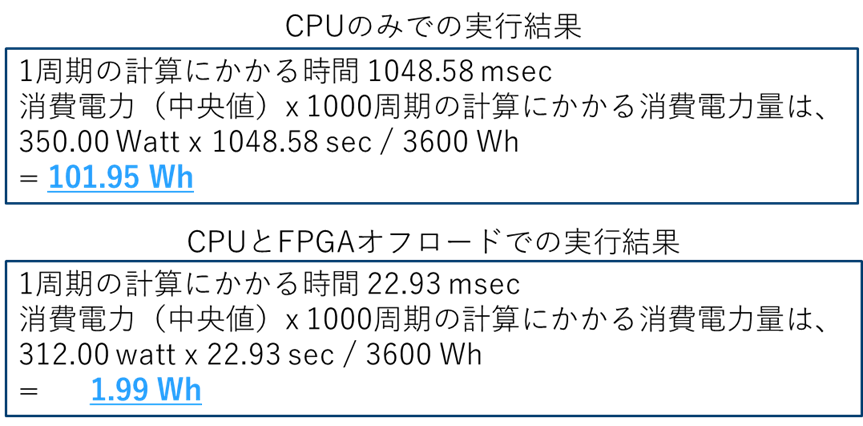

消費電力量の計算では、1周期の計算にかかった時間がmsecと比較的短い期間となります。計算を見やすくするため、あらかじめsec(秒)に換算しています。それぞれの消費電力から、1000周期を計算するのにかかる消費電力量を求めると、「CPUのみでの実行結果」では101.95 Whとなり、「CPUとFPGAオフロードでの実行結果」では1.99 Whといった結果が出ました。

図7.消費電力量の比較

これらの算出結果から実際にコストとして計算してみます。図6の結果をもとに計算しますが、電力量料金の単価は1 kWhとなっており、見やすくするために再度1000周期を積した計算量での比較をすることにしました。下記の図7での算出結果は、10^6周期分での比較した結果となりますが、それぞれの実行結果の計算量としては同じ量となります。

図8.コストパフォーマンスの比較

図8の結果をまとめると、同じ計算量でコストを比較したところ、FPGAオフロードを活用した場合、およそ98%のコスト削減効果が得られる結果となりました。また、計算にかかる時間(計算時間)を比較すると、FPGAオフロードを活用したほうがおおよそ46倍速く計算ができるという結果を得られました。

まとめ

今回の検証で得られた結果をまとめると、下記のようになります。

FPGAオフロードを活用した場合:

- 計算時間を46倍より高速に処理できる

- 同じ計算量で98%の電力代を節約可能

- Top 1精度は1%の差に抑えられる

- Top 5精度は6%の差が出た

今回の比較結果は、Mipsology Zebraのバージョンや、使用するニューラルネットワーク(今回はConvolutional Neural Network ResNet50)の種類によっても変わってきます。そのため、一概にこの結果がすべての環境で言えるわけではありません。また、FPGAのアルゴリズム(IPコア)のチューニングによっても改善したりできる余地はあります。

Mipsology社のZebraを活用した利点は、FPGAのIPコアをチューニングしていただき、今回のような結果を得られたことです。

最後に

今回の検証で分かったことは、FPGAオフロードはハードウェアの活用だけでなく、IPコアの効率化・チューニング次第でパフォーマンスを伸ばせることです。逆に言えば、FPGAを活用してもIPコアをチューニングできなければ、期待した効果は得られない可能性もあります。

また、FPGAの場合、用途によってボードのサイズを小さいものにしたり等、必要な場所によってカスタマイズすることができるのもFPGAを活用する利点になるかと考えています。Xilinx社のAlveoシリーズでは大容量の計算に対応したものから、小サイズのものまであります。例えば、データセンターでは大容量のボードを採用し、拠点や工場では小サイズのものを採用するといったことができます。

筆者プロフィール

Ryosunata Suhartono (スハルトノ リオスナタ)

ネットワンシステムズ株式会社 ビジネス開発本部

第1応用技術部 第1チーム 所属

キャンパスネットワーク、主にスイッチ製品の提案、導入支援業務を経験。ネットワークだけでなくトラフィック可視化製品も担当し、ネットワークとセキュリティを連携させたソリューションの検証なども経験。現在は、ローカル5Gだけでなく、エッジコンピューティングやP4テクノロジー等最新技術の評価検証業務に従事している。

■第三級陸上特殊無線技士保有

■CCIE R&S

Webからのお問い合わせはこちらから

ピックアップ

ナレッジセンターを検索する

カテゴリーで検索

タグで検索