- ナレッジセンター

- 匠コラム

通信システムでソフトエラーが発生!

- 匠コラム

- ネットワーク

ビジネス推進本部 応用技術部

コアネットワークチーム

関原 慎二

突然、ネットワーク機器が故障? でも電源を再起動したら直ってしまった。ハードウェアの不良でもなくソフトウェアのバグでもないのに・・・・。このような摩訶不思議な現象に遭遇していませんか。その原因の1つに宇宙から降り注ぐ中性子線の影響があります。中性子線はネットワーク機器に搭載するメモリ回路やロジック回路においてデータのビット反転を引き起こし、システムを停止させてしまいます。このような現象をソフトエラーと呼んでいます。今回は通信システムで発生するソフトエラーについてご紹介したいと思います。

(1) ソフトエラーってなに?

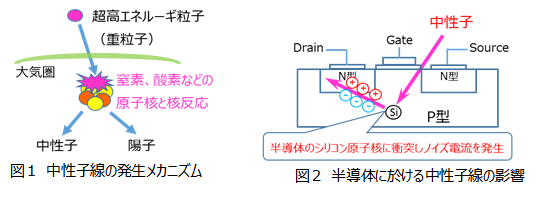

我々の身の回りには太陽光や紫外線など色々なものが宇宙より降り注いでいます。その中に中性子線というものがあります。これは宇宙で飛び回る超高エネルギー粒子(重粒子)が地球に突入した際に大気圏で窒素や酸素の原子核と核反応を起こしその結果、中性子線が飛散するというものです。降り注ぐ中性子線の量は太陽の黒点数と関係があります。北欧フィンランドにあるオウル大学では1964年から現在まで中性子線量の測定を行っておりその結果、約11年の周期で変化することが確認されています。中性子線量と太陽黒点数には相関関係があり太陽黒点数が少ないときに中性子線量は多くなります。また中性子線の密度は海面から約15kmの高さで最も多く、極地でも多くなります。この中性子線は容易に物体を通過し半導体デバイスのシリコン原子核に衝突し、その際に電荷を発生させます。この電荷により一時的にノイズ電流が流れSRAMメモリ(*1)やSRAM型FPGA(*2)のロジック回路のデータを1から0もしくは0から1にビット反転を引き起こします。このような現象をソフトエラーと呼び1個の中性子粒子で発生するソフトエラーをSEU(Single Event Upset)といいます。

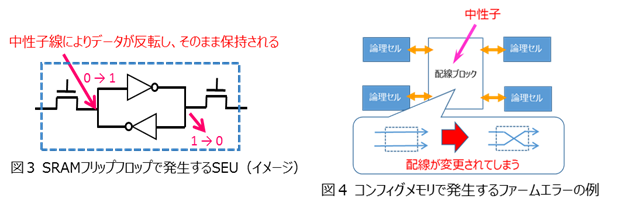

SEUは発生する箇所で大きく2種類に分類されます。一つはロジックの組み合わせ回路部分で発生する場合で、一時的なデータエラーを引き起こします。もう一つは記憶素子であるSRAMメモリやFPGAのSRAMフリップフロップ回路部分で発生する場合です。この場合はデータそのものが変更されてしまいます。特にFPGAの回路情報を保持するコンフィグメモリ内のSRAMフリップフロップで発生すると回路自体が変更されてしまいます。これをファームエラーと呼び、SRAM型FPGA特有のソフトエラーです。ファームエラーを回復させるためにはデバイスの再起動などを行いコンフィグメモリに本来の情報を上書きする必要があります。特に近年は半導体デバイスの微細化に伴い動作電圧の低電圧化が進んでおりソフトエラーが発生する確率は高くなっています。例えば、電源電圧が1.8Vから0.5Vなった場合、ソフトエラー発生率は約30倍になると言われています。

(2) ソフトエラーが通信システムに与える影響

ネットワークを支える通信システムの中でも、光伝送装置では半導体デバイスであるFPGAが数多く使用されています。これはコンフィグメモリ内容の書き換えを行うことで即座にFPGA回路の変更が可能となり、開発期間の短縮化によるコスト削減や仕様変更などに柔軟に対応することができるからです。しかしFPGA内部には前述のSRAM構成のフリップフロップが多数使用されている為にソフトエラーやファームエラーの影響を受け易くなってしまいます。通信システムで使用される光伝送装置でソフトエラーが発生した場合は以下のような影響が懸念されます。

①不具合事象が非再現となる

ソフトエラーによる不具合が原因で通信障害が発生した場合、そのアラームを保守者へ通知して該当の機器やモジュールを交換し通信の復旧を行います。その後、不具合となった機器やモジュールを製造メーカに返却して不具合解析を行いますが、事象が再現しない為に解析に時間とコストを要します。そして結果として原因が分からずじまいになってしまいます。

②不具合事象がサイレントアラームとなる

ファームエラーによりFPGAの回路構成情報であるコンフィグメモリ内容が書き換わってしまう

ケースでは不具合が故障として検出されず、保守者に何も通知されないサイレントアラーム状態

になってしまうことがあります。通常、光伝送装置では故障に備えて障害を検出する機能を具備しますが、ファームエラーの場合は回路そのものが変更されてしまうので思うような検出ができない場合があります。このようなケースでは大きな事態に発展する場合があります。

ここで1つのユースケースを紹介します。

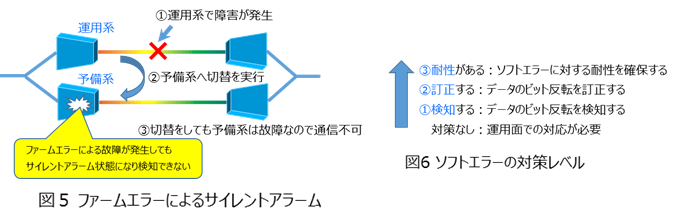

通信ネットワークでは障害発生時にサービスに与える影響を最小限にする目的で冗長化構成(2重化構成)を行います。そして運用している主系に障害が発生した場合は予備系へ切替えて通信を継続します。

ここで予備系の装置でファームエラーによる故障が発生してサイレントアラーム状態になってしまったケースにおいて、主系伝送路の障害等が発生した際に予備系では障害検知できていない(サイレントアラーム状態)なので、切り替え自体は行われますが予備系はソフトエラー故障の為に切り替えをしても通信ができません。即ち、冗長化機能が動作しない二重障害になってしまいます。

(3) ソフトエラーの影響を回避するには

ソフトエラーへの対応としては、部品面(FPGAなど)、装置設計面、装置運用面からのアプローチがあります。また対策レベルとしては、①検知レベル ②訂正レベル ③耐性レベルの3つに分類することができます。

①検知レベル

パリティビット(*3)を付加したメモリやCRCチェック(*4)回路などを使用することでデータのビット反転を検知します。

②訂正レベル

エラー訂正機能を持つECCメモリ(*5)やTMR(*6)などの多数決回路によりデータがビット反転した場合にデータの訂正を行います。また、定期的にコンフィグデータを上書きすることで動的かつ部分的にFPGAの再構成を行い、ビット反転となった場合でも一定時間後に正常な状態へ回復を行うDPR(Dynamic Partial Reconfiguration)タイプのFPGAも登場しています。

③耐性レベル

SRAM型でないフラッシュ型構造のFPGAや専用LSIであるASIC(*7)などを採用することでソフトエラーそのものに対する耐性を強化します。

また、ソフトエラー対策が十分になされていない装置については運用面でカバーしていきます。具体的には光伝送装置において通常のアラームに加え、装置性能情報やログを定期的に収集、監視を行い、装置動作上で有り得ない矛盾した状態と判断した場合にソフトエラー発生と推定しアラームを保守者へ通知します。その後、保守者は必要に応じて再起動などの対応を行います。

(4) ソフトエラー対策への取り組み

近年、ネットワーク機器の開発においてソフトエラー対策は必須となっています。国内ではTTC(一般社団法人情報通信技術委員会)において、ソフトエラー品質基準や設計基準、検証試験基準について標準化の取り組みを開始し国際電気通信連合の電気通信標準化部門(ITU-T)への提案も行っています。

まとめ

ソフトエラーの歴史は意外と古く1978年にインテルにより、そのメカニズムが明らかに

されています。そして近年ではSRAMメモリやFPGAなどの半導体の微細化による電源の低電圧化や大規模化に伴うトランジスタサイズの小型化により、ソフトエラーの影響をより受けやすくなっています。一方で再現性が極めて低い不具合事象を安易にソフトエラーと片づけてしまう風潮も見受けられます。通信システムの根幹を担う光伝送装置ではソフトエラーを検知して回避する手段が非常に重要になっています。

*1 SRAMメモリ:Static Random Access Memory

読み書きを自由に行える揮発性の半導体メモリで、電源を落とすとデータが失われる。

*2 SRAM型FPGA:Field-Programmable Gate Array

SRAMメモリセルにコンフィグレーション・データを保持するFPGAで、電源が投入されるとFlashメモリやEEPROMなどの外部記録メディアからデータをSRAMで構成するコンフィグレーションメモリーにロードする。データを書き換える事でカスタマイズしたの回路を実現する。

*3 パリティビット

データ通信などにおいて、データの誤り検出に用いられるパリティチェック(parity check)を行う為に、元のデータに一定の割合で付加するビット。

*4 CRCチェック:Cyclic Redundancy Check

誤り検出方式の一つで、データを値とみなして決められた定数で割った余り(余剰)を用いて受信データの誤りの検知を行う。

*5 ECCメモリ:ECCはError Correction Code

ソフトエラーやSEU(Single Event Upset)等の影響により誤った値が記録された場合、これをを検出し正しい値に訂正することができるメモリ。

*6 TMR:Triple Modular Redundancy

回路モジュールなどを3重化する冗長構成方式で、3つの出力の多数決結果により1個の

回路モジュールが故障しても正しい結果を得ることができる。また同時に出力同士を比較することで故障検出を可能にする。

*7 ASIC:Application Specific Integrated Circuit

特定の用途向けに設計、製造される専用の集積回路(LSI)。

執筆者プロフィール

関原 慎二

ネットワンシステムズ株式会社 ビジネス推進本部 応用技術部 コアネットワークチーム所属。

通信機メーカ入社後、キャリア向け伝送装置のハードウェア開発、LSI設計等に従事。

ネットワンシステムズではオプティカル製品(FTTH、WDM)の評価、検証及び案件技術支援を担当。

- ADVA Certified Expert #083193

- 工事担任者デジタル1種

Webからのお問い合わせはこちらから

ナレッジセンターを検索する

カテゴリーで検索

タグで検索